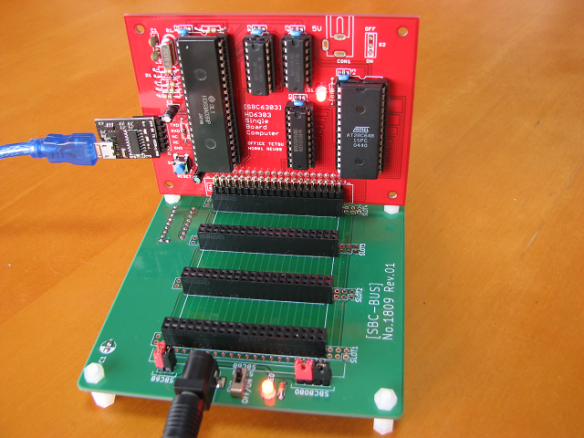

SBC68拡張ボードをSBC6303を使用して動作確認します。

SBC6303ルーズキットをSLOT4に実装します。

SBC6303単体の動作確認です。今回はALL CMOS化から74HC573を先日購入した74AS573に変更しました。

電源ONリセットも推薦環境ですので問題なし。リセットSWでの起動も問題ありません。

SBC-BUSに電源を接続しますのでSBC6303には電源用のスライドスイッチ&DCプラグは未実装です。

SBC-BUSはSBC6303の拡張端子に合わせていますが、デコード信号を追加している関係でSLOT4はSBC6303のA15,14,13から8000-9FFFh、A000-BFFFh、E000-FFFFhデコードした信号を追加しています。また、NMIはNCに、GND横のNCはP11,P13,P15,P17がつながっています。

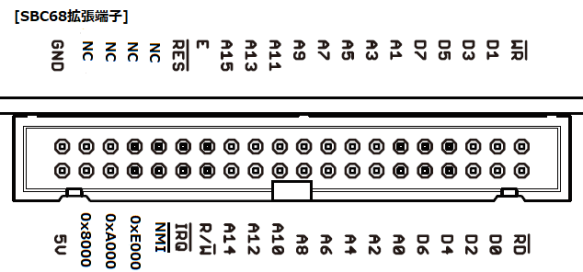

SBC6303ブートローダを追加します。

SBC6303ブートローダはSLOT2,3どちらに実装可能です。今回はSLOT2に実装しました。

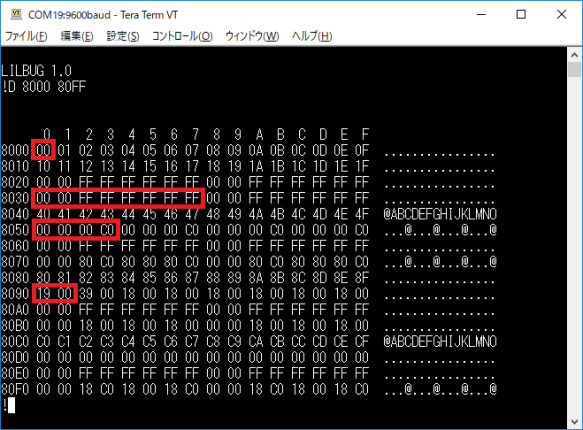

SBC6303ブートローダその6[拡張1 ]を実施した状態で32KバイトSRAM(M5M256DP-70LL)と128KバイトSRAM(HM628128ALP-7)でSDカードからLilbugが起動しそれぞれのメモリマップに対する動作をDコマンドとMコマンドを使用して確認しました。

簡易確認はOKです。また電源ONリセット、リセットSW(ほとんど押せない)ももちろんOKです。

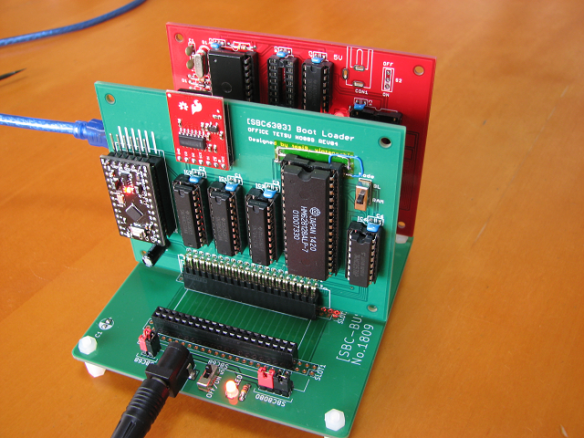

SBC6303の確認ができましたのでSBC6303を使用してSBC-I/Oの動作確認を行います。SBC-BUSはSBC6303の時は3スロット使用可能ですがSBC6303ブートローダのSBC-BUSの拡張2が未実施の為、現在は同時に使用できません。

SBC6303ルーズキットとSBC-I/Oの2枚構成でSBC-I/Oの動作確認を行います。

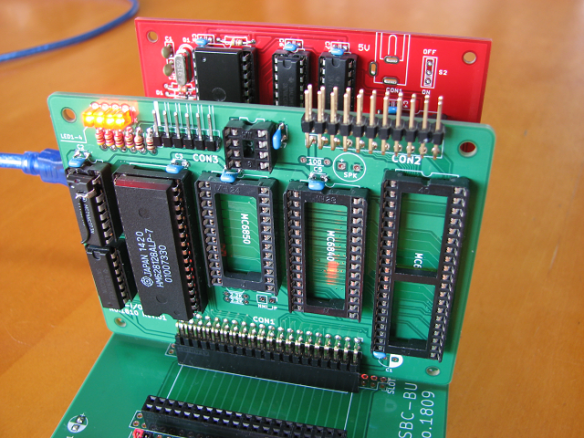

電源ONで74HC173に接続されたLED点灯しました。

74HC173は8000hのbit3-0に配置しているので8000hにFFhを書き込みましたが変化なし、何も考えずに00hを設定やっぱり変化なし。

SBC-BUS上の74HC138のアドレスの接続かデコード出力も誤ったと思たのですが結果はSBC-I/Oの74HC173のMr(リセット)の論理が逆でした。パターンがICソケットの下の為写真のように15ピンをGNDにICを加工しました。

これで8000hにFFhで消灯、00hで点灯、01h,02h,04h,08hと各LEDの点灯・消灯を確認してOKになりました。これでSBC-BUSのデコード回路が正しいことが確認できたので次はSRAMです。

SRAM(HM628128ALP-7)を実装してLilbugが起動することを確認しました。

DコマンドとMコマンドで簡易的に8000-9FFFh、E000-FFFFh以外がSRAMになっていることを確認してOK

MC6850/MC6840/MC6821はこれから確認予定です。

SBC-I/Oのアドレスデコードです。デコードにはゲートを使用せず各ICのCS端子でデコードしている関係で設定アドレス以外で競合が発生します。LEDの0番地はA4=0でデコードしている関係で周辺ICアクセス時はA4=1が条件になります。

デコード結果は下記になります。

LED 0x8000 (A4n) PTM 0x8030:37 (A5/A2:A0) PIA 0x8050:3 (A6+A4/A1:A0) ACIA 0x8090:91 (A7+A4/A0)

全ての周辺ICを搭載した時の8000h-80FFhのダンプ結果です。

MC6850(ACIA)のデコードを修正して周辺ICへのアクセスも問題ないようです。またパターンカット+ジャンパーが増えました。

<修正履歴>

- 74HC173の15ピンをVccからGNDに変更

- パターンカット一か所、ジャンパー1本

- MC6850(ACIA)のアドレスデコードエラー

- CS0=A4,CS1n=0x8000,CS2=A2で8014,5hにデコード

- PTMがA2-A0を使用している為競合

- CS0=A4,CS1n=0x8000,CS2=A7に変更で8090,91hにデコード